# 「インド半導体産業の展望」 -設計と後工程の潜在力に注目 -

三井物産戦略研究所 国際情報部アジア・大洋州室 ギリ ラム

## Summary

- インドの半導体産業は、設計、および検査・パッケージングなど後工程が急成長し、政府支援のもと 製造拠点の整備を進めているが、電力、原材料調達、人材、価格競争力などの課題が残る。

- 米Micronなどの後工程に加えて、印TATAによるチップの中身を作る前工程での大型投資が進行中で、 国内需要を起点に輸出拠点化を目指す。一方、台TSMC・韓Samsungの参入はまだ見込まれていない。

- インドの豊富な設計人材を強みに、欧米企業の設計拠点化が加速。半導体やEV・車載AI分野では日印企業の連携が期待され、長期的に見れば、日本企業にとってインドは、半導体製造拠点としての可能性を秘めた、有望なパートナーとなり得る。

#### 1. インドの半導体産業の成長と自立への挑戦

#### 1-1. 輸入依存から製造大国へ

インドは今、世界の半導体産業において存在感を高めるため、国家戦略として本格的な産業育成に乗り出している。スマートフォン、自動車、コンピューティング、データセンターなどの需要拡大を背景に、同国の半導体市場は2023年の5兆7,000億円から2030年には15兆円規模へと急成長する見通しである<sup>1</sup>。また、半導体産業は、地理的制約が少なく、国家安全保障や経済自立性の観点から「戦略資産」としての価値が高い。

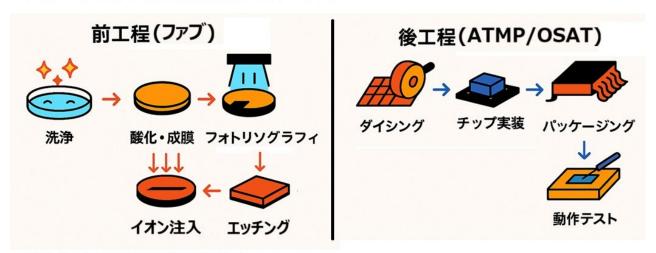

インドの半導体産業は現在、中国・台湾・韓国からの輸入に依存しており、特に、AI・5G・防衛など戦略分野において、国内での安定供給体制の構築が急務とされている。輸入依存からの脱却を図るため、設計からシリコンウェハー上に電子回路を形成する前工程(ファブリケーション)と、封入組立・検査して製品を仕上げる後工程(ATMP²/OSAT³)に至るまで、国内で一貫した生産体制を整備する方針だ(図表1)。

<sup>&</sup>lt;sup>1</sup> Press Information Bureau https://www.pib.gov.in/PressNoteDetails.aspx?id=154968&NoteId=154968&ModuleId=3

<sup>&</sup>lt;sup>2</sup> ATMP: Assembly, Testing, Marking and Packaging (半導体製造の後工程。チップの完成品化に必要な工程群)。

<sup>&</sup>lt;sup>3</sup> OSAT:Outsourced Semiconductor Assembly and Test (半導体後工程を専門とする外部企業によるサービス)。

図表1:半導体の前工程と後工程のイメージ図

出所: Copilot にて三井物産戦略研究所作成

こうした方針のもと、インド政府は2021年に「インド半導体ミッション (ISM)」を創設し、総額100億ドル (約1兆5,000億円)規模の支援策を通じて、設計エコシステムの育成から、前工程・後工程の製造拠点誘致を推進している。ISMの枠組みの下、政府は国内6州において10件の半導体製造案件の補助金申請を承認した。さらに4件が承認待ちであり、総投資額は182億ドル (約2兆7,300億円)に達する (図表2)。

| SN | 企業/案件                                      | 区分                         | 所在地                         | 投資予定額(億円) | 中央政府支援(額/根拠)                             |

|----|--------------------------------------------|----------------------------|-----------------------------|-----------|------------------------------------------|

| 1  | Micron Technology (ATMP)                   | ATMP/OSAT                  | グジャラート州サナンド                 | 4,125億円   | Capex50%最大 2,063億円<br>(ATMPスキームに基づく)     |

| 2  | Tata-PSMC Fab                              | シリコンCMOSファブ                | グジャラート州ドレラ                  | 1兆5,470億円 | 50% (対象Capexに対する政府<br>コミット。上限目安 7,735億円) |

| 3  | TSAT (Tata) Assam                          | ATMP/OSAT                  | アッサム州ジョルハット                 | 4,590億円   | 50%(上限目安 2,295億円)                        |

| 4  | CG Power & Industrial Solutions (OSAT)     | ATMP/OSAT                  | グジャラート州サナンド                 | 1,292億円   | 最大595億円(50%相当の補助<br>でFSA締結)              |

| 5  | Kaynes Semicon (OSAT)                      | ATMP/OSAT                  | グジャラート州サナンド                 | 561億円     | 50%(上限目安)                                |

| 6  | HCL-Foxconn JV(表示ドライバ)                     | 半導体製造(表示ドライバ<br>/OSAT工程含む) | UP州ジュワル<br>(ノイダNOIDA)       | 629億円     | 50%(上限目安)                                |

| 7  | SiCSem(SiC複合半導体)                           | コンパウンド (SiC) Fab+ATMP      | オディシャ州ブバネーシュワル              | 351億円     | 50%(上限目安)                                |

| 8  | 3D Glass Solutions (3DGS)                  | 先進パッケージ/埋込ガラス基板            | オディシャ州ブバネーシュワル              | 330億円     | 50%(上限目)                                 |

| 9  | CDIL (Continental Device)                  | ディスクリート/アナログ系能力拡充          | パンジャブ州モハリ                   | 20億円      | 50%(上限目安)                                |

|    | ASIP Technologies(APACT<br>提携)             | アドバンストSiP<br>(先進パッケージ)     | アンドラプラデシュ州<br>(ティルパティEMC想定) | 800億円     | 50%(上限目安)                                |

|    | 2025年9月                                    | 末までに政府の補助金申請中(未え           | <b></b>                     |           |                                          |

| SN | 企業/案件                                      | 区分                         | 所在地                         | 投資予定額(億円) | 最新マイルストーン(発表日)                           |

| 1  | UST / Kaynes Semicon(新<br>JV)              | 新設OSAT                     | グジャラート州サナンド                 | 560億円     | JV発表(2025/9/29)                          |

| 2  | Suchi Semicon                              | OSAT                       | グジャラート州スーラト                 | 150億円     | 施設開所(商用準備(2025/1<br>~))                  |

| 3  | RRP Electronics(ファブ計画)                     | 前工程(計画)                    | マハラシュトラ州ナビムンバイ              | 2,040億円   | 州が100エーカー土地供与LoC<br>(2025/9/12)          |

| 4  | Cyient Semiconductors /<br>Anora (量産テスト拠点) | 量産テスト/検証                   | カルナータカ州ベンガルール               | 未発表       | 新テストフロア発表(2025/9中旬)                      |

|    | 出所・A.K政体Droce Informa                      | ation Bureau の情報から三井物産     | <b>米</b> 胶研空配作成             |           |                                          |

これらの取り組みは、単なる産業政策にとどまらず、経済安全保障の一環として位置付けられている。また、インドが今後10年で半導体分野においてアジアの主要プレイヤーと肩を並べるための基盤を形成しようとするものである。

# 1-2. 印TATAと米Micronを中心に前・後工程のエコシステムを構築

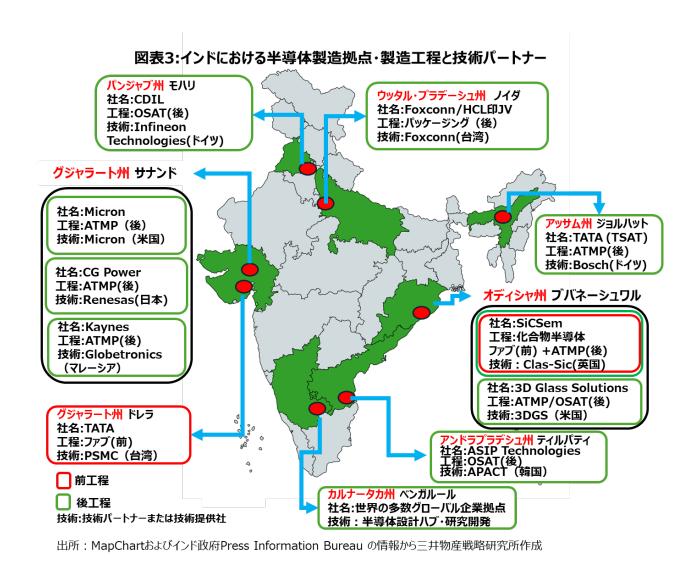

インドは半導体産業の前工程・後工程の両面で国家戦略に基づく基盤構築を急速に進めており、グジャラート州のドレラとサナンドがその中核拠点として台頭している(図表3)。前工程では、インドのTATAグループが半導体受託生産の売上高で世界6位台湾のPSMC<sup>4</sup>(力積電)との技術提携のもと、2027年の量産開始を目指し、インド初の半導体前工程工場をドレラに建設中である。総投資額は約1兆5,470億円に達し、28~120nmの成熟ノード<sup>5</sup>に対応する月産5万枚のウェハー生産を計画している。東京エレクトロンとの装置供給に関するMOUも締結済みで、オランダのASMLなどの装置メーカーも現地支援体制を整備中である。

<sup>&</sup>lt;sup>4</sup> PSMC: Powerchip Semiconductor Manufacturing Corporation 力晶積成電子製造股份有限公司ファウンドリー台湾の3位。

<sup>&</sup>lt;sup>5</sup> 成熟ノード (Mature Node):半導体製造プロセスにおいて、28nmより大きい比較的古い製造技術を用いた半導体チップ。

一方、後工程では、米国のMicronがサナンドにて半導体メモリDRAMおよびNAND製品の後工程工場を建設中であり、ISMの旗艦プロジェクトとして位置付づけられている。総額約4,125億円の投資のうち、Micron自身が約1,240億円を拠出し、残りの資金は、政府(中央および州)による助成制度を通じて提供される。2026年6月にPhase1の完成が予定されており、最大2万人の雇用創出が見込まれる。サナンド拠点ではMicronのほか、インドのKaynesやCG Powerも大規模な後工程ラインを立ち上げる計画を発表しており、図表2に示す中央政府による50%の支援に加え、州政府から20%の支援が加わることで、最大70%の政府支援を受けられる事例も出ている。

このような前工程・後工程の連携を踏まえ、TATAはグジャラート州のドレラで建設中の前工程で生産されたウェハーをアッサム州のジョルハットで建設中の後工程で仕上げる垂直統合型の事業戦略も視野に入れている。これにより、インド国内での一貫製造体制が構築され、自動車・家電・通信分野などの国内需要に対応しつつ、段階的な輸出展開も可能となる。

#### 1-3. 製造拠点としての課題

インドが、半導体の製造拠点として発展するには、インフラ、特に電力・水の供給、および原材料の安定供給体制の構築が重要となる。

電力供給に関しては、平均停電回数指標(SAIFI<sup>6</sup>)が、半導体後工程の拠点として先行するマレーシアの 0.49に対しインドは2.39と高く、平均停電継続時間もマレーシアの0.48時間に対してインドは3.72時間と 長く、その信頼性は低い。特にグジャラート州やアッサム州では、これらの数値がさらに悪化する傾向が ある。グジャラート州ドレラ地区の進出企業は、再生可能エネルギーとの併用や専用送電線、ディーゼル 発電機の併設などで対応を図っているものの、安定供給に不安が残る。

水に関しては、ドレラ地区の現地視察および聴き取り調査から、日本などの技術支援により、同地区の 半導体製造に必要な大量の超純水の供給体制は工場の操業開始までに整う見通しである。

原材料供給に関しては、現時点では半導体の前工程および後工程に必要な原材料の大半を輸入に依存している。しかし今後は、日本など外資との技術協力を強化し、原材料の国産化を段階的に推進することで、2030年代初頭には重要な原材料のサプライチェーンの自立性の確保を目指す(詳細は2-2参照)。これにより、地政学的リスクへの耐性を高め、国内半導体産業の持続的成長と競争力強化を図る。

#### 2. 設計ハブとしてのインドと日本企業との協業の可能性

## 2-1. グローバル企業が集うインドの半導体設計拠点

JLL Researchの報告によると、インドは世界のグローバル企業のITやR&Dを担う拠点(GCC<sup>7</sup>)の55%を占め

<sup>6</sup> 平均停電回数指標 (SAIFI): 1年間で顧客が経験する平均的な停電回数。電力の信頼性を評価する国際的な基準の1つ。

<sup>「</sup>GCC:Global Capability Center ITサービス、エンジニアリング、研究開発 (R&D) などの拠点。

る1,950拠点を有し、190万人以上の関連人材を擁している。ベンガルール、ハイデラバード、ノイダなどに形成されたGCCクラスターには、世界の約20%8のチップ設計エンジニアが集中しており、米国企業を中心に欧州、台湾、韓国、日本の各社がAI、車載、スマートフォン、IoT向けのSoC<sup>9</sup>や回路設計 (IP<sup>10</sup>)を展開している。

米国企業ではQualcommが約1万7,000人規模で技術開発や設計を進め、AMDは現在の約5,000人から2028年までに倍増して1万人体制の関連人材を配置する計画(図表4)で、欧州勢ではオランダのNXP、ドイツのInfineonが車載やIoT分野で設計体制を強化している。

| 企業名               | 本社地国名 | インド拠点場所        | 設計分野                       | 配置または配置予定の設計人材や研究員数      |

|-------------------|-------|----------------|----------------------------|--------------------------|

| AMD               | 米国    | ベンガルール         | HPC向けCPU/GPU/FPGA/SoC      | 約5,000人 →10,000人(~2028年) |

|                   |       | ベンガルール/ハイデラバード |                            |                          |

| Qualcomm          | 米国    | /チェンナイ/ノイダ     | 5Gモデム・SoC・車載/IoT           | 約17,000人(拠点拡張)           |

|                   |       | ベンガルール/        | 半導体・AI チップ設計/カスタム          |                          |

| NVIDIA            | 米国    | ハイデラバード/プネ     | AI チップの共同開発                | 約4,000人→10,000人計画        |

| Micron            | 米国    | ハイデラバード/ベンガルール | メモリ設計・検証                   | 約2,000人                  |

| Texas Instruments | 米国    | ベンガルール         | アナログ/DSP/MCU               | 約2,500人                  |

| Arm               | 英国    | ベンガルール/ノイダ     | CPU/IP、2nm設計               | 約2,000人                  |

|                   |       | ノイダ/ベンガルール/    |                            |                          |

| NXP               | オランダ  | ハイデラバード/プネ     | 車載/IoT/MCU                 | 約3,000人→6,000人(5年計画)     |

| Infineon          | ドイツ   | ベンガルール (他)     | 車載/パワー半導体R&D               | 約2,500人→5,000人(~2030年)   |

|                   |       | ノイダ/ベンガルール/    |                            |                          |

| Renesas           | 日本    | ハイデラバード/プネ     | 3nm設計·車載SoC                | 約1,000人                  |

| ROHM              | 日本    | ベンガルール/ノイダ/プネ  | パワー/アナログ、LSI設計/AE          | 約200人                    |

| Samsung SSIR      | 韓国    | ベンガルール         | メモリ/System LSI/Foundry系R&D | 約5,000人                  |

|                   |       | ベンガルール/ノイダ/    |                            |                          |

| MediaTek          | 台湾    | ムンバイ/デリー       | 無線/接続、スマホ/ホームSoC           | 約1,000人                  |

一方、インド国内で活躍する設計人材のうち日本企業が活用している割合は現状では5%<sup>11</sup>を下回り限定的だが、ルネサス エレクトロニクス、ソニー、東京エレクトロンなどが拠点を拡充中であり、今後の展開が期待される。なお、インド政府は、インド企業や研究機関が新しい半導体チップを設計する活動を支援するため、設計連動型支援策 (DLI<sup>12</sup>)のもとで、23件のチップ設計プロジェクトを承認 (図表5) した。

$<sup>^{8} \</sup>quad \text{https://bastionresearch.in/indias-leap-into-the-semiconductor-future-gradually-getting-ready-one-chip-at-at-ime/}$

<sup>&</sup>lt;sup>9</sup> SoC:System on a ChipはCPU、メモリ、GPU、通信モデムなどを、一つの半導体チップ(IC)上にすべて集積したもの。

<sup>10</sup> IP: (B-IST) チップ内部で自己診断を行う機能をもつIP やテスト容易性を高める設計資産 (DFT) IPなど。

<sup>11</sup> https://kasbusinessconsulting.com/global-capability-centers-indias-tech-leadership/

<sup>&</sup>lt;sup>12</sup> DLI: (Design Linked Incentive) スキームは、インド政府が半導体設計分野の支援制度で、国内設計エコシステムの強化とグローバル競争力の向上を目的としている。

図表5:設計連動型支援制度Design Linked Incentive (DLI) の下政府が承認した案件(総額約136億円)

| SN | 企業名                                               | テーマ(プロジェクト概要)                             |  |  |

|----|---------------------------------------------------|-------------------------------------------|--|--|

| 1  | DV2JS Innovation LLP                              | 低照度・単一光子検出対応の監視/車載カメラ向けイメージセンサー           |  |  |

| 2  | Vervesemi Microelectronics                        | モータ制御・スマート電力向けミックスドシグナルMCU                |  |  |

| 3  | Incise Infotech                                   | リニアLEDドライバIC                              |  |  |

| 4  | FermionIc Design                                  | 8-12GHzハイブリッドBF用4ch Mux/Demux G-P Shifter |  |  |

| 5  | Morphing Machines                                 | REDEFINEアーキ搭載SoC・IP・アクセラレータ               |  |  |

| 6  | Calligo Technologies                              | RISC-V+POSITコプロ搭載SoC+アクセラレータ              |  |  |

| 7  | Sensesemi Technologies                            | SenseSoC-200(IoT/医療)                      |  |  |

| 8  | Saankhya Labs(Tejas子会社)                           | 5G基地局向けベースバンドSoC                          |  |  |

| 9  | Aryabhata Circuits & Research Labs                | 先進タイヤ監視用IC                                |  |  |

| 10 | BigEndian Semiconductors                          | 監視向け映像/音声SoC                              |  |  |

| 11 | C2i Semiconductors                                | サーバ電源向けデジタル多相コントローラIC                     |  |  |

| 12 | MBit Wireless                                     | LTE Cat-1 bis & NB-IoTデュアルモードBBチップ        |  |  |

| 13 | MMRFIC Technology                                 | Ka帯レーダ用ビームフォーマIC                          |  |  |

| 14 | Sophrosyne Technologies                           | 心電/バイタル用超低消費SoC                           |  |  |

| 15 | Aheesa Digital Innovations                        | VEGAベースGPON/FTTxネットワークSoC                 |  |  |

| 16 | Mindgrove Technologies                            | Shakti系ビジョンSoC(エッジ向け)                     |  |  |

| 17 | InCore Semiconductors                             | RISC-Vマルチコア(スマホ/Edge-AI)                  |  |  |

| 18 | Netrasemi                                         | 高性能Edge-AI SoC(動画解析/ベクタ演算)                |  |  |

| 19 | Netrasemi                                         | 12nm/TSMC想定の64TOPS MLアクセラレータ              |  |  |

| 20 | Green PMU Semi                                    | エナジーハーベスティングPMU                           |  |  |

| 21 | WiSig Networks                                    | 陸上/衛星向けNB-IoT系SoC                         |  |  |

| 22 | MosChip Technologies(上場)                          | スマートエネルギーメータIC「VIDYUT」                    |  |  |

| 23 | Multi Nano Sense Technologies                     | MEMSガスセンサ+CMOS AFE SoC                    |  |  |

|    | 出所:インド政府Press Information Bureau の情報から三井物産戦略研究所作成 |                                           |  |  |

#### 2-2. 日印連携による半導体戦略と日本企業の貢献の可能性

日本とインドは、半導体供給網強化で2023年7月にパートナーシップを締結し、同分野において技術的補 完関係を生かした協調体制構築を目指している。日本企業は材料技術、製造装置、車載半導体、現場オペ レーションなどで世界的な競争力を持ち、一方、インドは豊富な設計人材と成長著しい電子機器市場を背 景に、グローバル設計ハブとしての地位を確立しつつある。

特に電動化(EV化)が進むインド市場では、パワー半導体や車載センサーの需要が急増しており、信頼性が高い日本の技術とインドの設計力を連携させることで、設計から製造までの一体型展開が可能となる。 これは両国にとって利益をもたらすだけでなく、サプライチェーンの強靭化にも寄与する。

すでにルネサス エレクトロニクスはインドに3nm設計拠点を設置し、車載SoC開発を強化。ソニーは AI・監視用途のイメージセンサー設計にインドの技術力を活用している。東京エレクトロンやSCREENは、

インド財閥企業との協業を通じて装置供給や技術のトレーニング拠点を構築し、人材育成にも貢献している。

インドでは前工程に加え、後工程分野も立ち上げ期にあることから、日本企業にとっては段階的な参入が現実的である。半導体産業は、極めて多様な原材料によって支えられており、材料の分野では日本企業が高い技術力と競争力を有する分野が多く(図表6)、今後インドの半導体産業育成の重要な役割を日本企業が担える。短期的には、材料・装置供給や品質管理支援が有効であり、中期的には小型化・高密度・高放熱性に優れているFC-BGA<sup>13</sup>やSIP<sup>14</sup>対応技術の現地化、東南アジアにある既存拠点との連携による事業継続計画 (BCP<sup>15</sup>)強化が視野に入る。

| 前工程(ファブリケーション)で使う主な材料 |                     |             |          |  |  |  |

|-----------------------|---------------------|-------------|----------|--|--|--|

| 分類                    | 主な材料                | 用途          | 日本企業の競争力 |  |  |  |

| <br>先端基板              | SOIウェハー             | 低消費電力/5G/車載 | 0        |  |  |  |

| フォトレジスト               | ArF/ KrF/ EUV       | 微細加工        | 0        |  |  |  |

| CMPスラリー               | 酸化·金属研磨剤            | 平坦化工程       | 0        |  |  |  |

| 高純度ガス                 | N2, H2, Ar, NH3     | プロセスガス      | 0        |  |  |  |

| 特殊ガス                  | WF6, SiH4, HBr, CF4 | CVD/エッチング   | 0        |  |  |  |

| 各種薬品                  | フッ酸, 過酸化水素          | 洗浄工程        | 0        |  |  |  |

| 化合物基板                 | SiC, GaN            | EV/パワー半導体   | 0        |  |  |  |

| シリコン基板                | シリコンウェハー            | 回路形成の基板     | 0        |  |  |  |

| エピタキシャル材料             | SiCIĽ               | パワーデバイス     | 0        |  |  |  |

| スパッタリングターゲット          | Cu, Ti, W           | 配線形成        | Δ        |  |  |  |

|                       | 後工程(ATMP/OSA        | T)で使われる主な材料 |          |  |  |  |

| 分類                    | 主な材料                | 用途          | 日本企業の競争力 |  |  |  |

| リードフレーム               | Cu/Fe-Ni合金          | パッケージの足     | 0        |  |  |  |

| モールド樹脂                | エポキシ封止材             | IC封止        | 0        |  |  |  |

| ボンディングワイヤ             | Au, Cu, Ag          | 電極接合        | 0        |  |  |  |

| ダイアタッチ材               | はんだ/銀ペースト           | チップ固定       | 0        |  |  |  |

| テープ                   | dicing tape         | チップ保護       | 0        |  |  |  |

| はんだボール                | Sn, Ag, Cu          | BGA用途       | 0        |  |  |  |

| EMC材料                 | エポキシ金型材             | 熱·湿気対策      | 0        |  |  |  |

|                       | ABF基板               | 高性能パッケージ    | Δ        |  |  |  |

|                       |                     |             |          |  |  |  |

<sup>&</sup>lt;sup>13</sup> FC-BGA (Flip Chip-Ball Grid Array) : 半導体チップを基板に接続する高密度パッケージ技術。

<sup>&</sup>lt;sup>14</sup> SIP: Session Initiation Protocol IP電話などで通話(セッション)の開始・変更・終了を制御するプロトコル。

<sup>&</sup>lt;sup>15</sup> BCP (Business Continuity Plan) :自然災害や地政学的リスクなどの緊急事態が発生した際に、企業の重要な事業を中断させずに継続・早期に復旧させるための計画。

インド政府も前述したようにDLIを通じて電子設計自動化 (EDA) ツールや新素材の研究開発を後押ししている。また、IITやIISc<sup>16</sup>などの主要教育機関に半導体研究センターを設置し、10万人規模の技術者育成計画も進行中。半導体の後工程では前工程に比べて自動化率が低く、依然として人手による作業が必要な工程が多いため、人材の豊富さはインドの競争力になる。こうした環境下での日印連携は、単なるコスト削減を超え、技術革新と経済関係の強化を進める重要な戦略軸となる。

# 3. インド半導体産業の展望

インドの半導体産業は、先述のように電力や水などのインフラに加え、原材料供給の課題を抱えながらも、政府支援を生かして技術力と産業基盤の強化を進めている。特に設計ならびに後工程においては成長余地が大きく、グローバル供給網における補完的な役割を担う可能性がある。EV、AI、通信分野での需要拡大や日米欧との連携を通じて、戦略的製造拠点としての地位確立が期待される。インドの自立的な供給体制の構築には段階的な投資、国際協力、人材育成が不可欠であり、少なくとも10年単位の長期的視野が求められる。これらの取り組みを通じて、インドは世界の半導体産業における重要な製造拠点へと成長する可能性を秘めている。

当レポートに掲載されているあらゆる内容は無断転載・複製を禁じます。当レポートは信頼できると思われる情報ソースから入手した情報・データに基づき作成していますが、当社はその正確性、完全性、信頼性等を保証するものではありません。当レポートは執筆者の見解に基づき作成されたものであり、当社および三井物産グループの統一的な見解を示すものではありません。また、当レポートのご利用により、直接的あるいは間接的な不利益・損害が発生したとしても、当社および三井物産グループは一切責任を負いません。レポートに掲載された内容は予告なしに変更することがあります。

<sup>&</sup>lt;sup>16</sup> IIT/IISc:Indian Institutes of Technology インド工科大学(インドのトップ理工系大学/ Indian Institute of Science インド理科大学院。